Параллельная обработка (реализация DSP) - Parallel processing (DSP implementation)

В цифровая обработка сигналов (DSP), параллельная обработка это метод дублирования функциональных единиц для одновременной работы с разными задачами (сигналами).[1] Соответственно, мы можем выполнять одну и ту же обработку для разных сигналы на соответствующие дублированные функциональные блоки. Далее, в силу особенностей параллельная обработка, конструкция параллельного DSP часто содержит несколько выходов, что дает более высокую пропускную способность, чем непараллельность.

Концептуальный пример

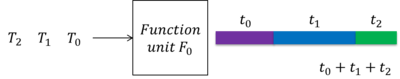

Рассмотрим функциональный блок (F0) и три задачи (Т0, Т1 и Т2). Требуемое время для функционального блока F0 обрабатывать эти задачи т0,т1 и т2 соответственно. Тогда, если мы выполним эти три задачи в последовательном порядке, время, необходимое для их выполнения, составит т0 + т1 + т2.

Однако, если мы продублируем функциональный блок еще на две копии (F) суммарное время сокращается до max (т0,т1,т2), что меньше, чем в последовательном порядке.

Против конвейерной обработки

Механизм:

- Параллельно: дублированные функциональные блоки, работающие параллельно

- Каждая задача полностью обрабатывается отдельным функциональным блоком.

- Конвейерная обработка: разные функциональные блоки работают параллельно

- Каждая задача разделена на последовательность подзадач, которые обрабатываются специализированными и различными функциональными блоками.

Цель:

- Конвейерная обработка приводит к сокращению критического пути, что может увеличить скорость выборки или уменьшить потребляемая мощность с той же скоростью, давая более высокую производительность на ватт.

- Методы параллельной обработки требуют нескольких выходных данных, которые вычисляются параллельно в период часов. Следовательно, эффективная скорость выборки увеличивается за счет уровня параллелизма.

Рассмотрим условие, при котором мы можем применять методы параллельной обработки и конвейерной обработки, лучше выбрать методы параллельной обработки по следующим причинам

- Конвейерная обработка обычно вызывает узкие места ввода-вывода

- Параллельная обработка также используется для снижения энергопотребления при использовании медленных часов.

- Гибридный метод конвейерной обработки и параллельной обработки еще больше увеличивает скорость архитектуры.

Параллельные КИХ-фильтры

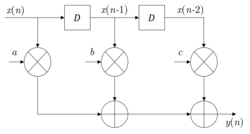

Рассмотрим трехконтактный КИХ-фильтр:[2]

который показан на следующем рисунке.

Предположим, что время вычисления единиц умножения равно Tм и та для добавления единиц. Период выборки определяется выражением

В результате распараллеливания получается следующая архитектура. Теперь частота дискретизации становится

где N - количество копий.

Обратите внимание, что в параллельной системе пока держится в конвейерной системе.

Параллельные БИХ-фильтры 1-го порядка

Рассмотрим передаточную функцию БИХ-фильтра 1-го порядка, сформулированную как

где |а| ≤ 1 для устойчивости, и такой фильтр имеет только один полюс, расположенный на z = а;

Соответствующее рекурсивное представление

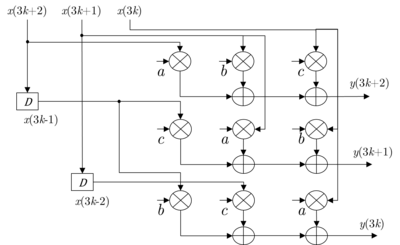

Рассмотрим проект 4-параллельной архитектуры (N = 4). В такой параллельной системе каждый элемент задержки означает задержку блока, а период тактовой частоты в четыре раза больше периода выборки.

Следовательно, повторяя рекурсию с п = 4k, у нас есть

Соответствующая архитектура показана следующим образом.

Результирующий параллельный дизайн имеет следующие свойства.

- Полюс оригинального фильтра находится на z = а в то время как полюс для параллельной системы находится на z = а4 что ближе к происхождению.

- Движение вехи повышает устойчивость системы к шуму округления.

- Аппаратная сложность этой архитектуры: N×N операции умножения-сложения.

Квадратное увеличение сложности оборудования может быть уменьшено за счет использования параллелизма и инкрементных вычислений, чтобы избежать повторных вычислений.

Параллельная обработка для малой мощности

Еще одно преимущество методов параллельной обработки состоит в том, что они позволяют снизить энергопотребление системы за счет снижения напряжения питания.

Учтите следующее энергопотребление в нормальной схеме CMOS.

где Cобщий представляет собой полную емкость схемы CMOS.

Для параллельной версии зарядная емкость остается прежней, но общая емкость увеличивается на N раз.

Чтобы поддерживать ту же частоту дискретизации, период тактовой частоты N-параллельная цепь увеличивается до N умноженное на задержку распространения исходной схемы.

Это увеличивает время зарядки N раз. Напряжение питания можно снизить до βV0.

Следовательно, потребляемая мощность N-параллельной системы может быть сформулирована как

куда β можно вычислить

Рекомендации

- ^ К. К. Пархи, Системы цифровой обработки сигналов СБИС: разработка и реализация, Джон Вили, 1999 г.

- ^ Слайды для систем цифровой обработки сигналов СБИС: разработка и реализация John Wiley & Sons, 1999 (номер ISBN: 0-471-24186-5): http://www.ece.umn.edu/users/parhi/slides.html