Удаление глюков - Glitch removal - Wikipedia

Удаление глюков устранение глюки - ненужные переходы сигналов без функциональности - от электронных схем. Рассеяние мощности затвора происходит двумя способами: статическое рассеяние мощности и динамическое рассеяние мощности. Мощность выброса зависит от динамического рассеивания в цепи и прямо пропорциональна коммутационной активности. Рассеиваемая мощность сбоев составляет 20% -70% от общей рассеиваемой мощности, и, следовательно, сбой следует исключить для конструкции с низким энергопотреблением.

Коммутационная активность происходит из-за сигнальные переходы которые бывают двух типов: функциональный переход и Сбой. Мощность переключения рассеивание прямо пропорционально коммутационной активности (α), нагрузке емкость (C), напряжение питания (В) и тактовая частота (ж) в качестве:

- P = α · C · V2·ж

Переключение активности означает переход на разные уровни. Сбои зависят от переходов сигналов, и большее количество сбоев приводит к более высокому рассеянию мощности. Согласно приведенному выше уравнению, рассеиваемая мощность переключения может контролироваться путем управления активностью переключения (α), масштабирование напряжения и Т. Д.

Методы уменьшения сбоев

Снижение коммутационной активности

Как обсуждалось, большее количество переходов приводит к большему количеству сбоев и, следовательно, к большему рассеянию мощности. Чтобы свести к минимуму возникновение сбоев, следует свести к минимуму переключение. Например, Код Грея может использоваться в счетчиках вместо бинарный код, поскольку каждое приращение в коде Грея меняет только один бит.

Замораживание ворот

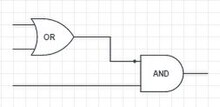

Замораживание ворот сводит к минимуму рассеяние мощности за счет устранения сбоев. Он полагается на наличие модифицированных стандартные библиотечные ячейки такие как так называемые F-ворота. Этот метод состоит из преобразования вентилей с высоким уровнем выбросов в модифицированные устройства, которые отфильтровывают выбросы при подаче управляющего сигнала. Когда управляющий сигнал высокий, F-Gate работает как обычно, но когда управляющий сигнал низкий, выход затвора отключается от земли. В результате он никогда не может быть разряжен до логического 0, и сбои не допускаются.

Фильтрация опасностей и задержка сбалансированного пути

Опасности в цифровых схемах - ненужные переходы из-за различных задержек пути в схеме. Методы задержки на сбалансированном пути могут использоваться для разрешения различных задержек на пути. Чтобы сделать задержки на пути равными, вставка буфера выполняется на более быстрых путях. Сбалансированная задержка пути позволит избежать сбоев на выходе.

Фильтрация опасностей - еще один способ устранения сбоев. В фильтрации опасностей ворота задержки распространения регулируются. Это приводит к уравновешиванию всех задержек пути на выходе.

Фильтрация опасностей предпочтительнее балансировки путей, поскольку балансировка путей потребляет больше энергии из-за вставки дополнительных буферов.

Размер ворот

Для балансировки пути используются методы увеличения и уменьшения размеров шлюза. Затвор заменяется логически эквивалентной ячейкой другого размера, так что задержка затвора изменяется. Поскольку увеличение размера затвора также увеличивает рассеиваемую мощность, увеличение размера затвора используется только тогда, когда мощность, сэкономленная за счет устранения сбоев, превышает рассеиваемую мощность из-за увеличения размера. Размер гейта влияет на глитч-переходы, но не влияет на функциональный переход.

Многопороговый транзистор

Задержка ворот является функцией его пороговое напряжение. Выбираются некритические пути и повышается пороговое напряжение затворов на этих путях. Это приводит к сбалансированной задержке распространения по разным путям, сходящимся в приемном шлюзе. Производительность сохраняется, поскольку она определяется временем, требуемым для критического пути. Более высокое пороговое напряжение также снижает ток утечки пути.

Смотрите также

- Конденсатор фильтра

- Изоляция операндов

- Рассеивание мощности процессора

- Динамическое масштабирование напряжения

- Стробирование часов

- Кодирование шины

- Аккумуляторная батарея

Рекомендации

дальнейшее чтение

- Хенгу, Ли; Хакгун, Шин; Джухо, Ким (2004). «Устранение сбоев путем замораживания ворот, определения размера ворот и вставки буфера для схемы оптимизации с низким энергопотреблением». 30-я ежегодная конференция Общества промышленной электроники IEEE, 2004 г. IECON 2004 г.. 3. С. 2126–2131. Дои:10.1109 / IECON.2004.1432125. ISBN 978-0-7803-8730-0.

- Кудерт, Оливье (сентябрь 1997 г.). "Размер ворот для ограниченной задержки / оптимизации мощности / площади". Транзакции IEEE в системах с очень крупномасштабной интеграцией (СБИС). 5 (4): 465–472. CiteSeerX 10.1.1.474.766. Дои:10.1109/92.645073.

- Sapatnekar, Sachin S .; Чжуан, Вэйтонг, Оптимизация задержки мощности при выборе размера ворот (PDF)

- Шум, Уоррен; Андерсон, Джейсон Х. (2011), Анализ и уменьшение мощности сбоев ПЛИС, Международный симпозиум по маломощной электронике и дизайну (ISLPED), стр. 27–32

- Чжаньпин, Чен; Liqiong, Wei; Кошик, Рой (март 1997 г.), Снижение выбросов и утечки мощности в схемах КМОП низкого напряжения, Школа электротехники и вычислительной техники Университета Пердью

внешняя ссылка

- Патент US6356101 B1: Цепь удаления сбоев, 2002-03-12, http://www.google.co.in/patents/US6356101.

- https://learn.digilentinc.com/Documents/277