МОЩНОСТЬ2 - POWER2

Эта статья включает в себя список общих использованная литература, но он остается в основном непроверенным, потому что ему не хватает соответствующих встроенные цитаты. (Сентябрь 2017 г.) (Узнайте, как и когда удалить этот шаблон сообщения) |

| Главная Информация | |

|---|---|

| Запущен | 1993 |

| Разработано | IBM |

| Архитектура и классификация | |

| Набор инструкций | POWER ISA |

| История | |

| Предшественник | МОЩНОСТЬ1 |

| Преемник | МОЩНОСТЬ3 |

| МОЩНОСТЬ, PowerPC, и Питание ISA архитектуры |

|---|

| NXP (ранее Freescale и Motorola) |

| IBM |

| IBM / Nintendo |

| Другой |

| Ссылки по теме |

| Отменено серым цветом, исторический курсивом |

В МОЩНОСТЬ2, первоначально названный RIOS2, это процессор разработано IBM который реализовал МОЩНОСТЬ архитектура набора команд. POWER2 был преемником МОЩНОСТЬ1, дебютировавшая в сентябре 1993 года в рамках IBM RS / 6000 системы. На момент своего появления POWER2 был самым быстрым микропроцессором, превосходящим Альфа 21064. Когда в 1993 году была представлена Alpha 21064A, POWER2 потерял лидерство и стал вторым. IBM заявила, что производительность POWER2 с частотой 62,5 МГц составила 73,3 SPECint92 и 134,6 SPECfp92.

Открытый исходный код Компилятор GCC удалена поддержка POWER1 (RIOS) и POWER2 (RIOS2) в версии 4.5.[1]

Описание

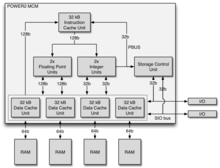

Усовершенствования по сравнению с POWER1 включали усовершенствования в архитектуре набора инструкций POWER (состоящей из новых пользовательских и системных инструкций и других функций, связанных с системой), более высокие тактовые частоты (от 55 до 71,5 МГц), дополнительные блок с фиксированной точкой и блок с плавающей запятой, больший кэш инструкций 32 КБ и больший кэш данных 128 или 256 КБ. POWER2 был многочиповой конструкцией, состоящей из шести или восьми полузаказной интегральные схемы, в зависимости от объема кэша данных (конфигурация 256 КБ требовала восьми микросхем). Разделение конструкции было идентично POWER1: микросхема блока кэширования команд, микросхема блока с фиксированной точкой, микросхема блока с плавающей запятой, микросхема блока управления памятью и две или четыре микросхемы блока кэширования данных.

Конфигурация из восьми кристаллов содержит в общей сложности 23 миллиона транзисторов и общую площадь кристалла 1215 мм.2. Чипы производятся IBM по технологии CMOS 0,72 мкм,[2] который имеет эффективную длину канала 0,45 мкм; и один слой поликремния и четыре слоя металлического межсоединения.[3] Чипы упакованы в керамический многокристальный модуль (MCM) размером 64 мм на 64 мм.

МОЩНОСТЬ2 +

Улучшенная версия POWER2, оптимизированная для обработка транзакции был представлен в мае 1994 года как POWER2 +. Рабочие нагрузки обработки транзакций выиграли от добавления кэша второго уровня емкостью 512 КБ, 1 МБ и 2 МБ. Этот кэш был реализован вне пакета со стандартными пакетными SRAM. Кэш был подключен к POWER2 + через 64- (для младших систем) или 128-битную шину (для high-end систем). Кеш был с прямым отображением, имел размер строки 128 байт и был сквозная запись. Теги кэша содержались на микросхеме блока управления хранилищем. POWER2 + имеет более узкую 64- или 128-битную шину памяти и меньший размер кэша данных на 64 или 128 КБ. Поскольку кэш-память меньше, микросхемы блока кэширования данных становятся меньше в результате, и обновленная микросхема блока управления памятью также меньше. Целью конфигурации с шестью микросхемами было снижение стоимости, поэтому микросхемы упакованы в шарик припоя connect (SBC) вместо MCM.

P2SC

P2SC для Суперчип POWER2, был выпущен в октябре 1996 года как преемник POWER2. Это была однокристальная реализация восьмичипового POWER2, объединяющая 15 миллионов транзисторов на 335-миллиметровом корпусе.2 кристалл изготовлен по пятислойному металлическому процессу CMOS-6S IBM 0,29 мкм. Первая версия работала на частоте 120 или 135 МГц, что почти в два раза быстрее, чем POWER2 на частоте 71,5 МГц, при этом шина памяти и ввода-вывода работала на половинной скорости для поддержки более высокой тактовой частоты. IBM заявила, что производительность этой версии была 5,5 SPECint95_base и 14,5 SPECfp95_base. Более быстрая деталь на 160 МГц, изготовленная по технологии CMOS-6S2 0,25 мкм, была анонсирована на форуме Microprocessor Forum в октябре 1997 года.

P2SC не был полной копией POWER2, кэша данных L1 и данных. резервный буфер перевода (TLB) емкость была уменьшена вдвое до 128 КБ и 256 записей соответственно, а редко используемая функция, блокирующая записи в TLB, не была реализована для того, чтобы уместить исходный дизайн на одном кристалле.

P2SC сменил МОЩНОСТЬ3 как флагманский микропроцессор IBM на RS / 6000 линия в 1998 году. Заметным использованием P2SC был 30-узловой IBM Темно-синий суперкомпьютер, победивший чемпиона мира Гарри Каспаров в шахматы в 1997 году. Однако возможности компьютера в игре в шахматы были обусловлены его специализированными интегральными схемами, а не P2SC.

Смотрите также

Примечания

- ^ «Серия выпусков GCC 4.5 - Изменения, новые функции и исправления - Проект GNU - Фонд свободного программного обеспечения (FSF)». gcc.gnu.org.

- ^ Гвеннап 1996

- ^ Белый 1994

использованная литература

- Barreh, J. I .; Golla, R.T .; Arimilli, L.B .; Джордан, П. Дж. (Сентябрь 1994 г.). «Блок кеширования инструкций POWER2». Журнал исследований и разработок IBM. 38 (5): 537–544. Дои:10.1147 / rd.385.0537.

- Болл, Ричард (15 октября 1997 г.). «Чипвилл США». Еженедельник электроники.

- ДеТар, Джим (22 августа 1994). «IBM подробно описывает Power2 +; DEC представляет новую Alpha AXP». Электронные новости.

- Гвеннап, Линли (4 октября 1993 г.). «IBM восстанавливает лидерство в производительности с помощью Power2». Отчет микропроцессора.

- Гвеннап, Линли (26 августа 1996 г.). «IBM превращает POWER2 в один чип». Отчет микропроцессора.

- Hicks, T. N .; Фрай, Р. Э .; Харви, П. Э. (сентябрь 1994 г.). «Модуль с плавающей запятой POWER2: Архитектура и реализация». Журнал исследований и разработок IBM. 38 (5): 525–536. Дои:10.1147 / rd.385.0525.

- Полузащитник, Дж. Роберт (28 июня 1993 г.). "IBM готовит RISC Progeny в Unix". Электронные новости.

- Шиппи, Дэвид (9 августа 1994). «Процессор Power2 +». Горячие чипсы 6.

- Шиппи, Д. Дж .; Гриффит Т. В. (сентябрь 1994 г.). «Блоки управления фиксированной точкой, кэшем данных и хранилищем POWER2». Журнал исследований и разработок IBM. 38 (5): 503–524. Дои:10.1147 / rd.385.0503.

- Статт, Пол (январь 1994). «Power2 берет на себя инициативу - пока». Байт.

- White, S.W .; Дхаван, С. (сентябрь 1994 г.). «POWER2: следующее поколение семейства RISC System / 6000». Журнал исследований и разработок IBM. 38 (5): 493–502. Дои:10.1147 / rd.385.0493.

дальнейшее чтение

- Вайс, Шломо; Смит, Джеймс Эдвард (1994). МОЩНОСТЬ и PowerPC. Морган Кауфманн. ISBN 1558602798. - Глава 6 описывает архитектуру и процессор POWER2.