Пиксельное визуальное ядро - Pixel Visual Core

В Пиксельное визуальное ядро (ПВХ) представляет собой серию На базе ARM система в упаковке (SiP) процессоры изображений разработано Google.[1] PVC - полностью программируемый изображение, зрение и AI многоядерная доменно-ориентированная архитектура (DSA) для мобильных устройств и в будущем для Интернет вещей.[2]Впервые он появился в Google Pixel 2 и 2 XL которые были представлены 19 октября 2017 года. Он также появился в Google Pixel 3 и 3 XL. Начиная с Pixel 4, этот чип был заменен на Пиксельное нейронное ядро.

История

Google ранее использовал Qualcomm Snapdragon с ЦПУ, GPU, Я ПУ, и DSP справиться со своим обработка изображений для них Google Nexus и Google Pixel устройств. С возрастающим значением компьютерная фотография методы, Google разработал Pixel Visual Core (PVC). Google утверждает, что PVC потребляет меньше энергии, чем использует ЦПУ и GPU будучи полностью программируемыми, в отличие от их блок обработки тензора (ТПУ) специализированная интегральная схема (ASIC) .Действительно, классический мобильные устройства оборудовать процессор сигналов изображения (ISP) - фиксированная функциональность обработка изображений трубопровод. В отличие от этого PVC имеет гибкие программируемые функции, не ограничиваясь только обработкой изображений.

ПВХ в Google Pixel 2 и 2 XL имеет маркировку SR3HX X726C502.[3]

ПВХ в Google Pixel 3 и 3 XL имеет маркировку SR3HX X739F030.[4]

Благодаря PVC Pixel 2 и Pixel 3 получили мобильную DxOMark из 98[5] и 101.[6]Последний - лучший мобильный телефон с одним объективом в рейтинге DxOMark, равный iPhone XR.[7]

Программное обеспечение Pixel Visual Core

Типичная программа обработки изображений PVC написана на Галогенид. В настоящее время он поддерживает только подмножество языка программирования Halide без операций с плавающей запятой и с ограниченными шаблонами доступа к памяти.[8]Галогенид - широко распространенный[нужна цитата ] специфичный для домена язык, который позволяет пользователю отделить алгоритм и планирование Таким образом, разработчик может написать программу, оптимизированную для целевой аппаратной архитектуры.[2]

Pixel Visual Core ISA

ПВХ имеет два типа архитектура набора команд (ISA), виртуальный и физический. Сначала программа на языке высокого уровня компилируется в виртуальный ISA (vISA), вдохновлен RISC-V ЭТО,[2] который полностью абстрагируется от целевого поколения оборудования. Затем программа vISA компилируется в так называемый физический ISA (pISA), это VLIW ЭТО. На этом этапе компиляции учитываются параметры целевого оборудования (например, размер массива PE, размер STP и т. Д.) И явно указываются перемещения памяти. Развязка ВИЗА и pISA позволяет первому быть кросс-архитектурным и независимым от поколения, в то время как pISA может быть скомпилирован в автономном режиме или через JIT-компиляция.[8]

Архитектура Pixel Visual Core

Pixel Visual Core представляет собой масштабируемую многоядерную энергоэффективную архитектуру с четным числом от 2 до 16 ядер.[2] Сердцевина ПВХ - это блок обработки изображений (IPU) программируемый блок, предназначенный для обработки изображений. Архитектура Pixel Visual Core также была разработана либо как отдельный чип, как SR3HX, либо как Блокировка IP за Система на микросхеме (SOC).[2]

Блок обработки изображений (IPU)

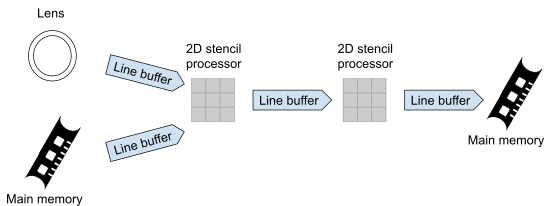

Ядро IPU имеет процессор трафаретов (STP), пул строчных буферов (LBP) и NoC. STP в основном обеспечивает 2-D SIMD массив обрабатывающих элементов (ПЭ), способных выполнять трафаретные вычисления, небольшая окрестность пикселей. Хотя похоже на систолический массив и вычисления волнового фронта, STP имеет явное программное управление перемещением данных. Каждый PE имеет 2x 16-битных арифметико-логические блоки (АЛУ), 1x 16 бит Умножитель-накопитель (МАК), 10x 16 бит регистры и 10 1-битных регистров предиката.[2]

Линейный буферный пул (LBP)

Учитывая, что одной из самых энергоемких операций является доступ к DRAM, каждый STP имеет временные буферы для увеличения. местонахождение данных, а именно LBP. Используемый LBP - это 2-D ФИФО который подходит для разных объемов чтения и записи. LBP использует поведенческую модель одного производителя и нескольких потребителей. Каждый LBP может иметь восемь логических блоков памяти LB и одну для DMA операции ввода-вывода.[8]Из-за действительно высокой сложности системы памяти разработчики PVC заявляют, что контроллер LBP является одним из самых сложных компонентов.[2]Используемый NoC - это кольцевая сеть на кристалле, используемая для связи только с соседними ядрами для экономии энергии и сохранения конвейерной вычислительной схемы.[2]

Обработчик трафаретов (STP)

STP имеет двумерный массив PE: например, массив 16x16 полных PE и четыре полосы упрощенных PE, называемых "гало"В STP есть скалярный процессор, называемый скалярной полосой (SCL), который добавляет управляющие инструкции с небольшой памятью команд. Последний компонент STP - это блок хранения загрузки, называемый генератором листов (SHG), где лист - это память PVC. блок доступа.[2]

Краткое описание конструкции SR3HX

PVC SR3HX имеет 64-битную ARMv8a. ARM Cortex-A53 ЦП, 8 ядер процессора изображений (IPU), 512 МБ LPDDR4, MIPI, PCIe. Количество ядер IPU по 512 арифметико-логические устройства (ALU), состоящий из 256 обрабатывающих элементов (PE), организованных в виде двумерного массива 16 x 16. Эти ядра выполняют пользовательский VLIW ISA. На каждый элемент обработки приходится два 16-битных ALU, и они могут работать тремя различными способами: независимым, объединенным и объединенным.[9] ПВХ SR3HX производится как Глоток к TSMC используя их 28 л.с. / мин HKMG процесс.[1] Он был разработан более 4 лет в партнерстве с Intel. (Кодовое имя: Монетт Хилл)[10] Google утверждает, что SR3HX PVC в 7-16 раз более энергоэффективен, чем Львиный зев 835.[1] И что SR3HX PVC может выполнять 3 триллиона операций в секунду, HDR + может работать в 5 раз быстрее и потреблять менее одной десятой энергии, чем Львиный зев 835.[11] Он поддерживает Галогенид для обработки изображений и TensorFlow для машинного обучения.[11]. Текущий чип работает на частоте 426 МГц, а один IPU может выполнять более 1 тераопс.[2][8]

Рекомендации

- ^ а б c Катресс, Ян. «Hot Chips 2018: живой блог Google Pixel Visual Core (10:00 по тихоокеанскому времени, 17:00 по всемирному координированному времени)». www.anandtech.com. Получено 2019-02-02.

- ^ а б c d е ж грамм час я j Хеннесси, Джон; Паттерсон, Дэвид (2017). Компьютерная архитектура: количественный подход (Шестое изд.). Морган Кауфманн. С. 579–606. ISBN 978-0-12-811905-1.

- ^ "Разборка Google Pixel 2 XL". я чиню это. 2017-10-19. Получено 2019-02-02.

- ^ "Разборка Google Pixel 3 XL". я чиню это. 2018-10-16. Получено 2019-02-02.

- ^ «Pixel 2 DxOMark».

- ^ «Pixel 3 DxOMark».

- ^ «iPhone XR DxOMark».

- ^ а б c d «Pixel Visual Core: полностью программируемый процессор изображений, машинного зрения и искусственного интеллекта Google для мобильных устройств. HotChips2018» (PDF).

- ^ "Pixel Visual Core (PVC) - Google - WikiChip". en.wikichip.org. Получено 2019-02-02.

- ^ «Google в партнерстве с Intel разработает чип Pixel Visual Core для Pixel 2». xda-developers. 2017-10-25. Получено 2019-02-02.

- ^ а б "Pixel Visual Core: обработка изображений и машинное обучение на Pixel 2". Google. 2017-10-17. Получено 2019-02-02.