Процессоры архитектуры MIPS - MIPS architecture processors - Wikipedia

Эта статья поднимает множество проблем. Пожалуйста помоги Улучши это или обсудите эти вопросы на страница обсуждения. (Узнайте, как и когда удалить эти сообщения-шаблоны) (Узнайте, как и когда удалить этот шаблон сообщения)

|

С 1985 года множество процессоров, реализующих ту или иную версию Архитектура MIPS были разработаны и широко используются.

Микропроцессоры MIPS

Первый микропроцессор MIPS, R2000, была анонсирована в 1985 году. Она добавила многоцикловые команды умножения и деления в несколько независимый блок на кристалле. Были добавлены новые инструкции для извлечения результатов из этого устройства обратно в файл регистра; эти инструкции по получению результатов были взаимосвязаны.

R2000 можно было загрузить либо прямой порядок байтов или же прямой порядок байтов. Он имел тридцать один 32-битный регистр общего назначения, но не регистр кода состояния (дизайнеры считали это потенциальным узким местом), и эта особенность разделяет его с 29000 драм и Альфа. В отличие от других регистров, счетчик команд не доступен напрямую.

R2000 также имел поддержку до четырех сопроцессоров, один из которых был встроен в основной ЦП и обрабатывал исключения, ловушки и управление памятью, а остальные три оставлены для других целей. Один из них может быть заполнен необязательным R2010 FPU, в котором было тридцать два 32-битных регистра, которые можно было использовать как шестнадцать 64-битных регистров для двойной точности.

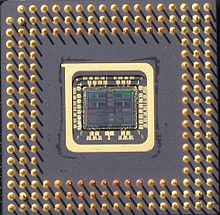

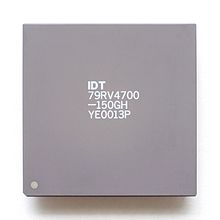

В R3000 сменил R2000 в 1988 году, добавив 32 КБ (вскоре увеличенных до 64 КБ) кешей для инструкций и данных, а также поддерживая разделяемую память. многопроцессорность в виде согласованность кеша протокол. Хотя в поддержке многопроцессорности R3000 были недостатки, она успешно использовалась в нескольких успешных многопроцессорных компьютерах. R3000 также имеет встроенный MMU, обычная особенность процессоров того времени. R3000, как и R2000, может работать в паре с R3010 FPU. R3000 был первым успешным разработчиком MIPS на рынке, и в итоге было выпущено более миллиона. Версия R3000 с увеличенной скоростью, работающая до 40 МГц, R3000A поставили 32 VUP (единицы производительности VAX). MIPS R3000A -совместимый R3051 на частоте 33,8688 МГц был процессор, используемый в Sony Игровая приставка хотя у него не было FPU или MMU. Сторонние разработки включают в себя Performance Semiconductor's R3400 и IDT R3500, оба они были R3000As со встроенным FPU R3010. Toshiba с R3900 был практически первым SoC для раннего карманные компьютеры это побежало Windows CE. А радиационно стойкий вариант для космических приложений, Мангуст-V, представляет собой R3000 со встроенным FPU R3010.

В R4000 серия, выпущенная в 1991 году, расширила MIPS до полной 64-битной архитектуры, переместила FPU на главный кристалл, чтобы создать однокристальный микропроцессор, и имела высокую тактовую частоту 100 МГц при введении. Однако для достижения тактовой частоты каждый кеш был уменьшен до 8 КБ, и для доступа к ним потребовалось три цикла. Высокие рабочие частоты были достигнуты за счет техники глубокая прокладка трубопроводов (в то время это называлось супер-конвейерной обработкой). Улучшенный R4400 за ним последовал в 1993 году. Он имел более крупные первичные кэши 16 КБ, в основном безошибочную 64-битную работу и поддержку большего размера кэша L2.

MIPS, ныне подразделение SGI под названием MTI, разработало недорогой R4200, основа для еще более дешевых R4300i. Производная от этого микропроцессора, NEC VR4300, использовался в Nintendo 64 игровая консоль.[1]

Устройства на квантовых эффектах (QED), отдельная компания, основанная бывшими сотрудниками MIPS, разработала R4600 Орион, то R4700 Орион, то R4650 и R5000. В то время как R4000 увеличил тактовую частоту и принес в жертву емкость кэша, в проектах QED упор делался на большие кеши, к которым можно было получить доступ всего за два цикла, и эффективное использование площади кремния. R4600 и R4700 использовались в недорогих версиях SGI Indy рабочая станция, а также первые маршрутизаторы Cisco на базе MIPS, такие как маршрутизаторы серий 36x0 и 7x00. В R4650 был использован в оригинале WebTV телеприставки (теперь Microsoft TV). В R5000 FPU имел более гибкое планирование с плавающей запятой одинарной точности, чем R4000, и в результате SGI Indys на базе R5000 имел гораздо лучшую графическую производительность, чем с аналогичной тактовой частотой. R4400 Indys с таким же графическим оборудованием. SGI дала старой графической плате новое имя, когда она была объединена с R5000 чтобы подчеркнуть улучшение. QED позже разработал RM7000 и RM9000 семейство устройств для рынков встраиваемых систем, таких как сетевые устройства и лазерные принтеры. QED был приобретен производителем полупроводников ЧВК-Сьерра в августе 2000 г. последняя компания продолжила инвестировать в архитектуру MIPS. В RM7000 Включает интегрированный кэш L2 размером 256 КБ и контроллер для дополнительного кэша L3. В RM9xx0 были семьей SOC устройства, которые включали Северный мост периферийные устройства, такие как контроллер памяти, PCI контроллер Гигабитный Ethernet контроллер и быстрый ввод / вывод, такой как Гипертранспорт порт.

В R8000 (1994) был первым суперскалярный Дизайн MIPS, способный выполнять две целочисленные или с плавающей запятой и две инструкции памяти за цикл. Дизайн был распределен по шести микросхемам: целочисленный блок (с 16 КБ инструкций и 16 КБ кэшей данных), блок с плавающей запятой, три полностью настраиваемых ОЗУ тегов вторичного кэша (два для доступа к вторичному кешу, один для отслеживания шины), и ASIC контроллера кеша. В конструкции было два полностью конвейерных блока умножения-сложения двойной точности, которые могли передавать данные из внекристального вторичного кэша объемом 4 МБ. R8000 работает на SGI POWER Challenge Серверы появились в середине 1990-х годов и позже стали доступны в рабочей станции POWER Indigo2. Хотя его производительность FPU достаточно хорошо подходит научным пользователям, его ограниченная целочисленная производительность и высокая стоимость снизили привлекательность для большинства пользователей, и R8000 был на рынке всего год и остается довольно редким.

В 1995 г. R10000 был выпущен. Этот процессор был однокристальным, работал на более высокой тактовой частоте, чем R8000, и имел более крупные кэши первичных инструкций и данных на 32 КБ. Он также был суперскалярным, но его главным нововведением было исполнение вне очереди. Даже с одним конвейером памяти и более простым FPU, значительно улучшенная целочисленная производительность, более низкая цена и более высокая плотность сделали R10000 предпочтительным для большинства клиентов.

Некоторые более поздние разработки были основаны на ядре R10000. В R12000 использовал процесс 0,25 микрометра для сжатия чипа и достижения более высоких тактовых частот. Пересмотренный R14000 разрешены более высокие тактовые частоты с дополнительной поддержкой DDR SRAM вне чипа тайник. Более поздние итерации называются 16000 рандов и R16000A и отличаются увеличенной тактовой частотой и меньшим объемом изготовления кристаллов по сравнению с предыдущими версиями.

Другие члены семейства MIPS включают R6000, ECL реализация произведена Биполярная интегрированная технология. R6000 представил архитектуру MIPS II. Его резервный буфер перевода (TLB) и архитектура кеша отличаются от всех других членов семейства MIPS. R6000 не дал обещанных преимуществ в производительности, и хотя он нашел некоторое применение в Контрольные данные машин, он быстро исчез с основного рынка.

История

Первое оборудование

В 1981 г. Джон Л. Хеннесси начал MIPS (Микропроцессор без взаимосвязанных ступеней конвейера) проект в Стэндфордский Университет исследовать RISC технологии. Результаты его исследований убедили его в будущем коммерческом потенциале технологии, и в 1984 году он взял творческий отпуск, чтобы основать Компьютерные системы MIPS. Компания разработала новую архитектуру, которую также назвали MIPS, и представил первую реализацию MIPS, R2000, в 1985 году. R2000 был улучшен, и дизайн был представлен как R3000 в 1988 году. Эти 32-разрядные процессоры составляли основу их компании на протяжении 1980-х годов и использовались в основном в SGI серия рабочие станции и позже Корпорация цифрового оборудования Рабочие станции и серверы DECstation. Коммерческие разработки SGI отклонились от Стэнфордского MIPS, реализовав большинство блокировок аппаратно, предоставляя полные инструкции умножения и деления (среди прочего). Частично проекты разрабатывались архитектором программного обеспечения. Эрл Киллиан который разработал 64-разрядное расширение набора инструкций MIPS III и руководил работой над микроархитектурой R4000.[2][3]

В 1991 году компания MIPS выпустила первую 64-битный микропроцессор, то R4000. Однако у MIPS возникли финансовые трудности при выводе его на рынок. Дизайн был настолько важен для SGI, в то время одного из немногих основных клиентов MIPS, что SGI выкупила компанию в 1992 году, чтобы гарантировать, что дизайн не будет утерян. Как дочерняя компания SGI, компания стала известна как MIPS Technologies.

Лицензируемая архитектура

В начале 1990-х MIPS начала лицензировать свои разработки сторонним поставщикам. Это оказалось довольно успешным из-за простоты ядра, что позволило использовать его в ряде приложений, которые раньше использовали гораздо менее функциональные CISC конструкции аналогичных количество ворот и цена - эти два понятия тесно связаны; цена ЦП обычно зависит от количества вентилей и внешних контактов. Sun Microsystems пытались добиться аналогичного успеха, лицензируя свои SPARC core, но не был таким успешным. К концу 1990-х годов MIPS была локомотивом в встроенный процессор поле. По данным MIPS Technologies Inc., рост наблюдался экспоненциально: в 1997 г. было поставлено 48 миллионов процессоров на базе MIPS и 49% от общей доли рынка процессоров RISC.[4] MIPS был настолько успешным, что SGI выделила MIPS Technologies в 1998 году. Полностью половина доходов MIPS сегодня поступает от лицензирования их проектов, в то время как большая часть остального поступает от контрактных работ по проектированию ядер, которые затем будут производиться третьими сторонами.

В 1999 году компания MIPS Technologies заменила предыдущие версии архитектуры MIPS двумя архитектурами: 32-разрядной. MIPS32 (на основе MIPS II с некоторыми дополнительными функциями из MIPS III, MIPS IV и MIPS V) и 64-разрядной версии MIPS64 (на основе MIPS V) для лицензирования. NEC, Toshiba и SiByte (позже приобретен Broadcom ) каждый получил лицензии на MIPS64, как только об этом было объявлено. Philips, LSI Logic и IDT с тех пор присоединились к ним. Сегодня ядра MIPS являются одними из наиболее часто используемых «тяжеловесных»[требуется разъяснение ] ядра на рынке компьютерных устройств (карманные компьютеры, приставки и др.).

Поскольку архитектура MIPS лицензируется, она привлекла несколько процессорных запускать компании на протяжении многих лет. Одним из первых стартапов по разработке процессоров MIPS был Устройства на квантовых эффектах (см. следующий раздел). Команда разработчиков MIPS, разработавшая R4300i основал компанию SandCraft, который разработал R5432 для NEC и позже произвел SR71000, один из первых внеочередное исполнение процессоры для встраиваемого рынка. Оригинал DEC Сильная рука В итоге команда разделилась на два стартапа на базе MIPS: SiByte, который произвел SB-1250, один из первых высокопроизводительных MIPS на базе системы на кристалле (SOC); пока Алхимия Полупроводник (позже приобретен AMD ) произвел Au-1000 SoC для маломощных приложений. Лексра использовал MIPS-подобно архитектура и добавленные расширения DSP для рынка аудиочипов и многопоточность поддержка сетевого рынка. Из-за того, что Lexra не лицензировала архитектуру, между двумя компаниями было возбуждено два судебных процесса. Первое было быстро решено, когда Lexra пообещала не рекламировать свои процессоры как MIPS-совместимые. Второй (о патенте MIPS 4814976 для обработки невыровненного доступа к памяти) был затяжным, нанес ущерб бизнесу обеих компаний и завершился тем, что MIPS Technologies предоставила Lexra бесплатную лицензию и крупный платеж наличными.

Появились две компании, специализирующиеся на строительстве. многоядерный устройства, использующие архитектуру MIPS. Raza Microelectronics, Inc. приобрела линейку продуктов у вышедшего из строя SandCraft, а затем произвела устройства с восемью ядрами, предназначенные для рынков телекоммуникаций и сетей. Cavium, первоначально производитель процессоров безопасности также производил устройства с восемью ядрами ЦП, а затем и с 32 ядрами для тех же рынков. Обе эти компании разработали свои ядра собственными силами, просто лицензируя архитектуру, вместо того, чтобы покупать ядра у MIPS.

Рабочий стол

Среди производителей компьютеров рабочая станция системы, использующие процессоры MIPS, являются SGI, MIPS Computer Systems, Inc., Рабочие станции Whitechapel, Olivetti, Сименс-Никсдорф, Acer, Корпорация цифрового оборудования, NEC, и DeskStation.

Операционные системы портированная на архитектуру включает SGI IRIX, Microsoft с Windows NT (через v4.0), Windows CE, Linux, FreeBSD, NetBSD, OpenBSD, UNIX Система V, SINIX, QNX, и собственная компания MIPS Computer Systems RISC / OS.

В начале 1990-х было предположение, что MIPS и другие мощные RISC процессоры обогнали бы Intel IA-32 архитектура. Этому способствовала поддержка первых двух версий Microsoft с Windows NT за Альфа, MIPS и PowerPC - и в меньшей степени Архитектура клиппера и SPARC. Однако, поскольку Intel быстро выпустила более быстрые версии своих Pentium CPU класса, Microsoft Windows NT v4.0 отказался от поддержки чего-либо, кроме IA-32 и Alpha. С SGI решение о переходе на Itanium и архитектуры IA-32 в 2007 г. (после банкротства в 2006 г.[5]) и приобретение в 2009 г. Rackable Systems, Inc., поддержка потребительского рынка MIPS / IRIX прекратилась в декабре 2013 года, как первоначально планировалось. Тем не менее, группа поддержки все еще существует для особых случаев и отремонтированных систем, которые все еще доступны в ограниченном количестве.[6]

Встроенные рынки

В течение 1990-х годов архитектура MIPS получила широкое распространение на рынке встраиваемых систем, в том числе для использования в компьютерная сеть, телекоммуникации, видео аркадные игры, игровые приставки, компьютерные принтеры, цифровой телеприставки, цифровые телевизоры, DSL и кабельные модемы, и персональные цифровые помощники.

Низкое энергопотребление и тепловые характеристики встроенных реализаций MIPS, широкая доступность встроенных инструментов разработки и знание архитектуры означают, что использование микропроцессоров MIPS во встроенных ролях, вероятно, останется обычным явлением.

Синтезируемые ядра для рынков встраиваемых систем

В былые времена[когда? ] большая часть технологий, используемых в различных поколениях MIPS, предлагалась как IP-ядра (строительные блоки) для встроенный процессор конструкции. Обе 32-битный и 64-битный предлагаются базовые ядра, известные как 4K и 5K. Эти ядра можно смешивать с дополнительными модулями, такими как FPUs, SIMD системы, различные устройства ввода / вывода и т. д.

Ядра MIPS были коммерчески успешными и теперь используются во многих потребительских и промышленных приложениях. Ядра MIPS можно найти в более новых Cisco, Linksys и маршрутизаторы роутеров Mikrotik, кабельные модемы и ADSL модемы, смарт-карты, лазерный принтер двигатели, телеприставки, роботы, и портативные компьютеры. В мобильных телефонах и КПК MIPS в значительной степени не смогла вытеснить действующего, конкурирующего ARM архитектура.

Процессоры архитектуры MIPS включают: IDT RC32438; ATI / AMD Ксиллеон; Алхимия Au1000, 1100, 1200; Broadcom Sentry5; RMI XLR7xx, Cavium Octeon CN30xx, CN31xx, CN36xx, CN38xx и CN5xxx; Infineon Technologies EasyPort, Amazon, Danube, ADM5120, WildPass, INCA-IP, INCA-IP2; Технология микрочипов PIC32; NEC EMMA и EMMA2, NEC VR4181A, VR4121, VR4122, VR4181A, VR4300, VR5432, VR5500; Дубовые Технологии Поколение; ЧВК-Сьерра RM11200; QuickLogic QuickMIPS ESP; Toshiba Донау, Toshiba TMPR492x, TX4925, TX9956, TX7901; КОМДИВ-32, КОМДИВ-64, ELVEES Multicore из России.

Суперкомпьютеры на базе MIPS

Одним из наиболее интересных приложений архитектуры MIPS является ее использование в суперкомпьютерах с большим количеством процессоров. Силиконовая Графика (SGI) переориентировала свой бизнес с настольных графических рабочих станций на высокопроизводительные вычисления рынок в начале 1990-х гг. Успех первого набега компании на серверные системы, Испытание серии на базе R4400 и R8000, и позже R10000, побудило SGI создать значительно более мощную систему. Внедрение интегрированного R10000 позволило SGI создать систему, Происхождение 2000, в конечном итоге масштабируемый до 1024 ЦП, используя его NUMAlink cc-NUMA межсоединение. Происхождение 2000 породило Origin 3000 серия, которая превысила максимальное количество ЦП 1024, но с использованием чипов R14000 и R16000 до 700 МГц. Ее суперкомпьютеры на базе MIPS были сняты с производства в 2005 году, когда SGI приняла стратегическое решение перейти на архитектуру Intel IA-64.

Стартап в области высокопроизводительных вычислений под названием SiCortex представила суперкомпьютер на базе массового параллелизма MIPS в 2007 году. Машины основаны на архитектуре MIPS64 и имеют высокопроизводительное межсоединение с использованием Граф Каутца топология. Система очень энергоэффективна и вычислительно мощна.[нужна цитата ] Самым инновационным аспектом системы был ее многоядерный узел обработки, который объединяет шесть ядер MIPS64, поперечный переключатель контроллер памяти, соединить DMA двигатель, Гигабитный Ethernet и PCI Express все контроллеры на одном кристалле, который потребляет всего 10 Вт энергии, но имеет пиковую производительность с плавающей запятой 6 гигафлопс. Самая мощная конфигурация, SC5832, представляет собой суперкомпьютер с одним шкафом, состоящий из 972 таких узловых микросхем, что в общей сложности составляет 5832 процессорных ядра MIPS64 и максимальная производительность 8,2 терафлопс.

Loongson

Loongson семейство MIPS-совместимых микропроцессоров, разработанных Китайская Академия Наук 'Институт вычислительной техники (ИКТ). В первых моделях, независимо разработанных китайцами, не было поддержки четырех инструкций, запатентованных MIPS Technologies.[7] В июне 2009 года компания ICT лицензировала архитектуры MIPS32 и MIPS64 от MIPS Technologies.[8] Начиная с 2006 года, ряд компаний выпустили компьютеры на базе Loongson, в том числе неттопы и нетбуки разработан для использования с низким энергопотреблением.[9][10]

В последние годы специальный чип Loongson (1E04 / 1E0300 / 1E1000,1F04 / 1F0300,1J) использовался на 3-5 навигационных спутниках Beidou.

Рассвет 6000

Рассвет 6000 суперкомпьютер, прогнозируемая производительность которого превышает 1PFLOPS, будет использовать Loongson процессор. Dawning 6000 в настоящее время разрабатывается совместно компаниями ICT и Dawning Information Industry. Ли Гоцзе, председатель компании Dawning Information Industry и директор и академик ICT, сказал, что исследования и разработки Dawning 6000, как ожидается, будут завершены через два года. Ожидается, что к тому времени высокопроизводительные компьютеры китайского производства совершат два крупных прорыва: во-первых, внедрение процессоров отечественного производства; во-вторых, существующая кластерная системная структура высокопроизводительных компьютеров будет изменена, когда производительность достигнет 1 PFLOPS.

MIPS Aptiv

Объявлен в 2012 году,[11] Семейство MIPS Aptiv включает три 32-разрядных процессора, основанных на архитектуре MIPS32 Release 3.

microAptiv

microAptiv[12] представляет собой компактное встроенное процессорное ядро реального времени с пятиступенчатым конвейером и набором команд сжатия кода microMIPS. microAptiv может быть сконфигурирован как микропроцессор (microAptiv UP) с кэшами инструкций и данных и блоком управления памятью, либо как микроконтроллер (microAptiv UC) с блоком защиты памяти. ЦП объединяет функции DSP и SIMD для удовлетворения требований к обработке сигналов для встраиваемых сегментов начального уровня, включая промышленное управление, интеллектуальные счетчики, автомобильную и проводную / беспроводную связь.

interAptiv

interAptiv[13] - это многопроцессорное ядро, использующее девятиступенчатый конвейер с многопоточностью. Ядро может использоваться для высокопараллельных приложений, требующих оптимизации затрат и энергопотребления, таких как интеллектуальные шлюзы, обработка основной полосы частот в пользовательском оборудовании LTE и малых сотах, контроллеры SSD и автомобильное оборудование.

proAptiv

proAptiv[14] представляет собой суперскалярное ядро процессора, вышедшее из строя, доступное в одно- и многоядерных версиях продукта. proAptiv разработан для обработки приложений в подключенной бытовой электронике и обработки уровня управления в сетевых приложениях.

MIPS воин

Объявлено в июне 2013 г.,[15] Семейство MIPS Warrior включает несколько 32-разрядных и 64-разрядных процессоров, основанных на архитектурах MIPS Release 5 и 6.

Воин М-класса

32-битные ядра MIPS для встраиваемых приложений и микроконтроллеров:

- Ядра MIPS M5100 и MIPS M5150 (MIPS32 Release 5):[16] пятиступенчатая конвейерная архитектура, microMIPS ISA, модуль MIPS DSP R2, быстрая обработка прерываний, расширенные возможности отладки / профилирования и управление питанием.

- Ядра MIPS M6200 и M6250 (MIPS32 Release 6):[17] шестиступенчатая конвейерная архитектура, microMIPS ISA, выделенный модуль DSP и SIMD

Воин I класса

64-битные процессоры MIPS для высокопроизводительных встраиваемых приложений с низким энергопотреблением:

- Многопроцессорное ядро MIPS I6400 (MIPS64 Release 6):[18] одновременная многопоточность (SMT), аппаратная виртуализация, 128-битный SIMD, расширенное управление питанием, мультиконтекстная безопасность, возможность расширения до согласованной работы с несколькими кластерами.

Воин P-класса

32-битные и 64-битные процессоры приложений MIPS:

- Многопроцессорное ядро MIPS P5600 (MIPS32 Release 5):[19] аппаратная виртуализация с обходом аппаратной таблицы, 128-битной SIMD, 40-битной расширенной физической адресацией (XPA)

- Многопроцессорное ядро MIPS P6600 (MIPS64 Release 6): аппаратная виртуализация с аппаратным обходом таблиц, 128-битный SIMD

Смотрите также

Рекомендации

- ^ NEC предлагает два высокопроизводительных 64-разрядных микропроцессора RISC

- ^ "Эрл Киллиан". Паравиртуальный. 26 ноября 2010. Архивировано с оригинал 13 февраля 2012 г.. Получено 26 ноября 2010.

- ^ "Выпускники суперкомпьютера S-1: Эрл Киллиан". Университет Клемсона. 28 июня 2005 г.. Получено 26 ноября 2010.

В ранней работе Эрла Киллиана ... В качестве директора по архитектуре MIPS он разработал 64-битное расширение набора инструкций MIPS III и руководил работой над микроархитектурой R4000. Он был соучредителем компании QED, создавшей процессоры MIPS R4600 и R5000. Совсем недавно он был главным архитектором в Tensilica, работая над конфигурируемыми / расширяемыми процессорами.

- ^ «Брошюра MIPS» (PDF). MIPS Technologies Inc.. Получено 2 марта, 2013.

- ^ Патрик Фицджеральд (6 мая 2006 г.). «Silicon Graphics ищет главу 11 по мере снижения продаж». Wall Street Journal.

- ^ «Окончание общедоступности продуктов MIPS® IRIX®». 2013.

- ^ Китайская дилемма микропроцессоров

- ^ «Китайский институт компьютерных технологий лицензирует стандартные архитектуры MIPS». Архивировано из оригинал на 2011-05-08. Получено 2017-04-21.

- ^ "Статья LinuxDevices о Municator". Архивировано из оригинал на 2012-12-16.

- ^ "Yeelong Технические характеристики ». LinuxDevices. 22 октября 2008 г. Архивировано с оригинал 10 декабря 2012 г.

- ^ С, Ганеш Т. "MIPS Technologies обновляет линейку IP процессоров с помощью серии Aptiv". www.anandtech.com. Получено 2016-06-22.

- ^ «Ядро процессора microAptiv - Imagination Technologies». Воображение Технологии. Получено 2016-06-22.

- ^ «InterAptiv Processor Core - Imagination Technologies». Воображение Технологии. Получено 2016-06-22.

- ^ «ProAptiv Processor Core - Imagination Technologies». Воображение Технологии. Получено 2016-06-22.

- ^ «Представляем процессорные ядра MIPS Series5 'Warrior': новая революция в области IP процессоров от Imagination - Imagination Technologies». Воображение Технологии. 2013-06-26. Получено 2016-06-22.

- ^ "Семейство ядер M-Class M51xx - технологии воображения". Воображение Технологии. Получено 2016-06-22.

- ^ "Процессорные ядра M-Class M6200 и M6250 - Imagination Technologies". Воображение Технологии. Получено 2016-06-22.

- ^ "Многопроцессорное ядро I-Class I6400 - Imagination Technologies". Воображение Технологии. Получено 2016-06-22.

- ^ «Многопроцессорное ядро P-Class P5600 - Imagination Technologies». Воображение Технологии. Получено 2016-06-22.