Регистр сдвига - Shift register - Wikipedia

А регистр сдвига это тип цифровая схема используя каскад шлепки где выход одного триггера соединен со входом следующего. Они разделяют один тактовый сигнал, что заставляет данные, хранящиеся в системе, перемещаться из одного места в другое. При подключении последнего триггера обратно к первому, данные могут циклически перемещаться внутри переключателей в течение длительных периодов времени, и в этой форме они использовались как форма память компьютера. В этой роли они очень похожи на более ранние память линии задержки системы и широко использовались в конце 1960-х - начале 1970-х годов для замены этой формы памяти.

В большинстве случаев несколько параллельных регистров сдвига будут использоваться для создания большего пула памяти, известного как "битовый массив ". Данные сохранялись в массиве и считывались параллельно, часто как компьютерное слово, в то время как каждый бит последовательно сохранялся в регистрах сдвига. При разработке битовых массивов существует неизбежный компромисс; размещение большего количества триггеров в ряд позволяет одному устройству сдвига хранить больше бит, но требует большего количества тактовых циклов, чтобы протолкнуть данные через все переключатели, прежде чем данные могут быть снова прочитаны.

Регистры сдвига могут иметь оба параллельно и серийный входы и выходы. Они часто конфигурируются как «последовательный вход, параллельный выход» (SIPO) или «параллельный вход, последовательный выход» (PISO). Есть также типы с последовательным и параллельным входом и типы с последовательным и параллельным выходом. Также существуют «двунаправленные» регистры сдвига, которые позволяют сдвиг в обоих направлениях: L → R или R → L. Последовательный вход и последний выход регистра сдвига также могут быть соединены для создания «циклического регистра сдвига». Регистр PIPO (параллельный вход, параллельный выход) работает очень быстро - выход выдается в течение одного тактового импульса.

Последовательный вход и выход (SISO)

Разрушительное считывание

| 0 | 0 | 0 | 0 | 0 |

|---|---|---|---|---|

| 1 | 1 | 0 | 0 | 0 |

| 2 | 0 | 1 | 0 | 0 |

| 3 | 1 | 0 | 1 | 0 |

| 4 | 1 | 1 | 0 | 1 |

| 5 | 0 | 1 | 1 | 0 |

| 6 | 0 | 0 | 1 | 1 |

| 7 | 0 | 0 | 0 | 1 |

| 8 | 0 | 0 | 0 | 0 |

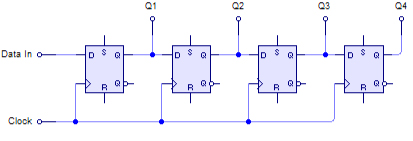

Это простейшие регистры сдвига. Строка данных представлена как «Data In» и сдвигается вправо на одну ступень каждый раз, когда запускается «Data Advance». высоко. При каждом продвижении крайний левый бит (т.е. «Data In») сдвигается в первый резкий поворот вывод. Крайний правый бит (т.е. «Data Out») сдвигается и теряется.

Данные сохраняются после каждого резкий поворот на выходе "Q", поэтому в этой конфигурации доступно четыре "слота" памяти, следовательно, это 4-битный регистр. Чтобы дать представление о схеме сдвига, представьте, что регистр содержит 0000 (так что все слоты памяти пусты). Поскольку «Data In» представляет 1,0,1,1,0,0,0,0 (в этом порядке, каждый раз с импульсом в «Data Advance» - это называется синхронизацией или стробированием) в регистр, это результат. Правый столбец соответствует выходному выводу самого правого триггера и т. Д.

Таким образом, последовательный вывод всего регистра равен 00001101. Можно видеть, что если бы данные продолжали вводить, они бы получили именно то, что были введены (10110000), но смещены на четыре цикла «Data Advance». Это устройство является аппаратным эквивалентом очередь. Кроме того, в любое время весь регистр может быть установлен в ноль, установив контакты сброса (R) в высокий уровень.

Эта аранжировка выполняет разрушительное считывание - каждая система данных теряется после того, как она была сдвинута из крайнего правого бита.

Последовательный вход и параллельный выход (SIPO)

Эта конфигурация позволяет преобразовать последовательный формат в параллельный. Ввод данных является последовательным, как описано в разделе SISO выше. После того, как данные были синхронизированы, они могут быть либо считаны на каждом выходе одновременно, либо их можно сдвинуть.

В этой конфигурации каждый триггер срабатывает край. Все триггеры работают на заданной тактовой частоте. Каждый входной бит направляется к N-му выходу после N тактов, что приводит к параллельному выходу.

В случаях, когда параллельные выходы не должны изменяться в процессе последовательной загрузки, желательно использовать защелкивающиеся или буферизованный выход. В регистре сдвига с защелкой (например, 74595 ) последовательные данные сначала загружаются во внутренний буферный регистр, а затем после получения сигнала загрузки состояние буферного регистра копируется в набор выходных регистров. В общем, практическое применение сдвигового регистра последовательного ввода / параллельного вывода состоит в преобразовании данных из последовательного формата на одном проводе в параллельный формат на нескольких проводах.

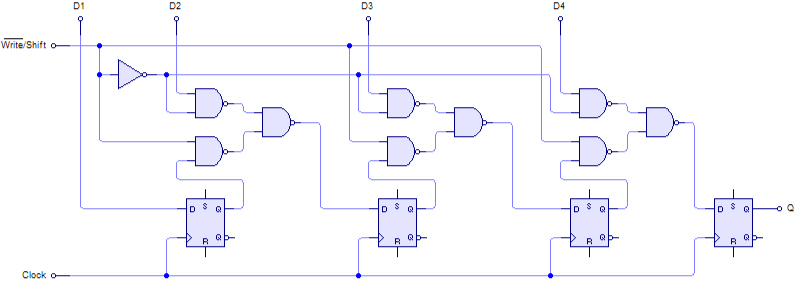

Параллельный вход и последовательный выход (PISO)

В этой конфигурации данные вводятся в строках с D1 по D4 в параллельном формате, причем D1 является самым старшим битом. Чтобы записать данные в регистр, контрольная строка записи / сдвига должна находиться в НИЗКОМ состоянии. Чтобы сдвинуть данные, линия управления W / S переводится в ВЫСОКИЙ уровень, а регистры синхронизируются. Теперь устройство действует как сдвиговый регистр PISO с D1 в качестве входа данных. Однако до тех пор, пока количество тактов не превышает длину строки данных, выход данных Q будет считаться параллельными данными по порядку.

На анимации ниже показана последовательность записи / сдвига, включая внутреннее состояние сдвигового регистра.

Использует

Одно из наиболее распространенных применений сдвигового регистра - преобразование между последовательным и параллельным интерфейсами. Это полезно, так как многие схемы работают с группами битов параллельно, но последовательные интерфейсы проще построить. Регистры сдвига могут использоваться как простые схемы задержки. Несколько двунаправленных регистров сдвига также могут быть подключены параллельно для аппаратной реализации куча.

Регистры SIPO обычно присоединяются к выходу микропроцессоров, когда больше универсальный ввод / вывод булавки необходимы, чем есть в наличии. Это позволяет управлять несколькими двоичными устройствами, используя только два или три контакта, но медленнее, чем при параллельном выходе. Рассматриваемые устройства подключаются к параллельным выходам сдвигового регистра, и желаемое состояние для всех этих устройств может быть отправлено из микропроцессора с помощью одного последовательного соединения. Точно так же конфигурации PISO обычно используются для добавления большего количества двоичных входов к микропроцессору, чем доступно - каждый двоичный вход (например, кнопка или более сложная схема) подключается к параллельному входу сдвигового регистра, затем данные отправляются обратно через последовательный к микропроцессору, используя на несколько строк меньше, чем требовалось изначально.

Регистры сдвига также могут использоваться как расширители импульсов. По сравнению с моностабильными мультивибраторами, синхронизация не зависит от значений компонентов, однако для этого требуются внешние часы, а точность синхронизации ограничена степенью детализации этих часов. Пример: Ронья Твистер, где пять регистров сдвига 74164 образуют ядро временной логики таким образом (схематический ).

В ранних компьютерах регистры сдвига использовались для обработки данных: два числа, которые нужно было добавить, хранились в двух регистрах сдвига и синхронизировались в арифметико-логический блок (АЛУ) с результатом, возвращаемым на вход одного из регистров сдвига (аккумулятор), который был на один бит длиннее, поскольку двоичное сложение может привести только к ответу того же размера или на один бит длиннее.

Многие компьютерные языки включают инструкции для «сдвига вправо» и «влево» данных в регистре, эффективно разделяя на два или умножая на два для каждого сдвигаемого места.

Очень большие регистры сдвига с последовательным входом и выходом (размером в тысячи бит) использовались аналогично предыдущим. память линии задержки в некоторых устройствах, построенных в начале 1970-х гг. Такие воспоминания иногда называли «циркулирующей памятью». Например, Datapoint 3300 терминал хранил свой дисплей из 25 строк 72 колонки символов верхнего регистра с использованием пятидесяти четырех 200-битных регистров сдвига, расположенных в шести дорожках по девять пакетов в каждой, обеспечивая хранение 1800 шестибитных символов. Конструкция регистра сдвига означала, что прокрутку дисплея терминала можно было выполнить, просто приостановив вывод дисплея, чтобы пропустить одну строку символов.[1]

История

Один из первых известных примеров сдвигового регистра был в Mark 2. Колосс, машина для взлома кода, построенная в 1944 году. Это было шестиступенчатое устройство, построенное из вакуумные трубки и тиратроны.[2] Регистр сдвига также использовался в Машина IAS, построен Джон фон Нейман и другие на Институт перспективных исследований в конце 1940-х гг.

Смотрите также

- Память линии задержки

- Регистр сдвига с линейной обратной связью (LFSR)

- Счетчик звонков

- СерДес (Сериализатор / десериализатор)

- Шина последовательного периферийного интерфейса

- Таблица поиска регистра сдвига (SRL)

- Круглый буфер

Рекомендации

- ^ bitsavers.org, DataPoint 3300 Руководство по техническому обслуживанию, Декабрь 1976 г.

- ^ Цветы, Томас Х. (1983), «Дизайн Колосса», Анналы истории вычислительной техники, 5 (3): 246, Дои:10.1109 / MAHC.1983.10079