Физический дизайн (электроника) - Physical design (electronics)

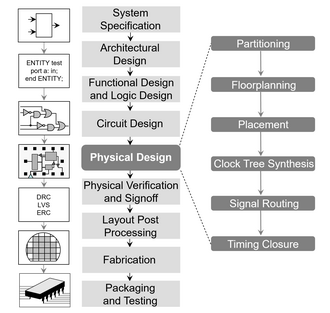

В конструкция интегральной схемы, физический дизайн это шаг в стандартном цикле проектирования, который следует после схемотехника. На этом этапе схемные представления компонентов (устройств и межсоединений) конструкции преобразуются в геометрические представления форм, которые при изготовлении из соответствующих слоев материалов обеспечат требуемое функционирование компонентов. Это геометрическое представление называется макет интегральной схемы. Этот шаг обычно разбивается на несколько подэтапов, которые включают в себя как проектирование, так и проверку и проверку макета.[1][2]

Современный день Интегральная схема (IC) дизайн разделен на Front-end дизайн с использованием HDL и Внутренний дизайн или же Физический дизайн. Входными данными для физического проектирования являются (i) список соединений, (ii) библиотечная информация об основных устройствах в проекте и (iii) технологический файл, содержащий производственные ограничения. Физический дизайн обычно заканчивается Постобработка макета, в котором вносятся изменения и дополнения в схему размещения микросхемы.[3] Далее следует Изготовление или же Производственный процесс где конструкции переносятся на кремниевые кристаллы, которые затем упаковываются в ИС.

С каждой из упомянутых выше фаз связаны проектные потоки. Эти потоки проектирования определяют процесс и руководящие принципы / структуру для этого этапа. В процессе физического проектирования используются технологические библиотеки, предоставляемые производственными предприятиями. Эти технологические файлы содержат информацию о типе используемой кремниевой пластины, используемых стандартных элементах, правилах компоновки (например, ДРК в СБИС) и др.

Подразделения

Обычно физическая конструкция ИС подразделяется на полный обычай и полу-нестандартный дизайн.

- Полностью настраиваемый: конструктор имеет полную гибкость при разработке макета, предопределенные ячейки не используются.

- Semi-Custom: предварительно разработанные ячейки библиотеки (желательно протестированные с DFM ), разработчик имеет гибкость в размещении ячеек и маршрутизации.[4]

Можно использовать ASIC для полного индивидуального дизайна и FPGA для потоков проектирования Semi-Custom. Причина в том, что можно гибко проектировать / изменять блоки дизайна из библиотек, предоставленных поставщиком в ASIC.[5] Эта гибкость отсутствует для Semi-Custom Flows с использованием FPGA (например, Альтера ).

Схема физического проектирования ASIC

Основные шаги в ASIC потоками физического проектирования являются:

- Дизайн Netlist (после синтеза)

- Планировка этажей

- Разбиение

- Размещение

- Синтез дерева часов (CTS)

- Маршрутизация

- Физическая проверка

- Постобработка макета с генерацией данных маски

Эти шаги - только основы. Существуют подробные потоки PD, которые используются в зависимости от используемых инструментов и методологии / технологии. Некоторые из инструментов / программного обеспечения, используемых при разработке серверной части:

- Cadence (компилятор Cadence Encounter RTL, цифровая реализация Encounter, решение Cadence Voltus IC Power Integrity, решение Cadence Tempus Timing Signoff)

- Synopsys (компилятор дизайна, компилятор IC II, валидатор IC, PrimeTime, PrimePower, PrimeRail)

- Магма (BlastFusion и др.)

- Mentor Graphics (Olympus SoC, IC-Station, Калибр)

Поток физического проектирования ASIC использует технологические библиотеки, предоставляемые производителями. Технологии обычно классифицируются по минимальному размеру элемента. Стандартные размеры, в порядке миниатюризации: 2мкм, 1 мкм, 0,5 мкм, 0,35 мкм, 0,25 мкм, 180нм, 130нм, 90нм, 65нм, 45нм, 28нм, 22нм, 18нм, 14нм и т. Д. Их также можно классифицировать по основным производственным подходам: n-скважинный процесс, двухскважинный процесс, ТАК ЧТО Я процесс и др.

Дизайн списка соединений

Физический дизайн основан на списке соединений, который является конечным результатом процесса синтеза. Synthesis преобразует дизайн RTL, обычно закодированный на VHDL или Verilog HDL, в описания на уровне шлюза, которые следующий набор инструментов может прочитать / понять. Этот список соединений содержит информацию об используемых ячейках, их взаимосвязях, используемой области и другие детали. Типичные инструменты синтеза:

- Компилятор Cadence RTL / Врата сборки / Физически осведомленный синтез (PKS)

- Компилятор дизайна Synopsys

В процессе синтеза применяются ограничения, чтобы гарантировать, что проект соответствует требуемой функциональности и скорости (спецификациям). Только после того, как список соединений проверен на функциональность и синхронизацию, он отправляется в поток физического проектирования.

Шаги

Планировка этажей

Второй шаг в процессе физического проектирования: планировка этажа. Планировка этажа - это процесс определения структур, которые следует размещать близко друг к другу, и распределения для них пространства таким образом, чтобы соответствовать иногда противоречивым целям доступного пространства (стоимость чипа), требуемой производительности и желания иметь все близко ко всему остальному.

На основе области дизайна и иерархии выбирается подходящий план этажа. Планировка этажа учитывает используемые в проекте макросы, память, другие IP-ядра и их размещение, возможности маршрутизации, а также площадь всей конструкции. Планировка этажа также определяет структуру ввода-вывода и соотношение сторон дизайна. Плохая планировка приведет к неэффективному использованию площади кристалла и перегрузке трассы.

Во многих методологиях проектирования площадь и скорость являются предметом компромиссов. Это связано с ограниченными ресурсами маршрутизации, поскольку чем больше используется ресурсов, тем медленнее выполняется операция. Оптимизация для минимальной площади позволяет конструкции использовать меньше ресурсов и обеспечивает большую близость секций конструкции. Это приводит к более коротким межсоединениям, меньшему количеству используемых ресурсов маршрутизации, более быстрым сквозным сигнальным трактам и даже более быстрому и более согласованному времени места и маршрута. Если все сделано правильно, то к планировке нет никаких негативных последствий.

Как правило, разделы пути данных больше всего выигрывают от планирования этажа, в то время как случайная логика, конечные автоматы и другая неструктурированная логика могут быть безопасно оставлены на усмотрение раздела размещения программного обеспечения места и маршрута.

Пути данных обычно являются областями проекта, в которых несколько битов обрабатываются параллельно, причем каждый бит изменяется одинаково, возможно, с некоторым влиянием соседних битов. Примеры структур, составляющих пути данных: сумматоры, вычитатели, счетчики, регистры и мультиплексоры.

Разбиение

Разделение - это процесс разделения чипа на небольшие блоки. Это делается в основном для разделения различных функциональных блоков, а также для упрощения размещения и трассировки. Разделение может быть выполнено на этапе проектирования RTL, когда инженер-проектировщик разделяет весь проект на подблоки, а затем приступает к проектированию каждого модуля. Эти модули связаны друг с другом в основном модуле, называемом модулем TOP LEVEL. Такой вид разбиения обычно называется логическим разбиением. Цель разделения - разделить схему таким образом, чтобы количество соединений между разделами было минимальным.

Размещение

Перед началом оптимизации размещения все модели нагрузки на провода (WLM) удаляются. Размещение использует значения RC из виртуального маршрута (VR) для расчета времени. VR - это кратчайшее манхэттенское расстояние между двумя кеглями. VR RC более точны, чем WLM RC.

Размещение выполняется в четыре этапа оптимизации:

- Оптимизация перед размещением

- В оптимизации размещения

- Оптимизация пост-размещения (PPO) до синтеза дерева часов (CTS)

- PPO после CTS.

- Оптимизация перед размещением оптимизирует список соединений перед размещением, HFN (High Fanout Nets) сворачиваются. Это также может уменьшить размеры ячеек.

- Оптимизация на месте повторно оптимизирует логику на основе VR. Это может выполнять определение размера ячейки, перемещение ячейки, обход ячейки, разделение цепей, дублирование ворот, вставку буфера, восстановление области. Оптимизация выполняет итерацию исправления настройки, инкрементного времени и размещения, управляемого перегрузкой.

- Оптимизация размещения после того, как CTS выполнит оптимизацию списка соединений с идеальными часами. Он может исправить нарушения настройки, удержания, максимального количества транзакций / ограничений. Он может оптимизировать размещение на основе глобальной маршрутизации. Это синтез HFN.

- Оптимизация размещения поста после CTS оптимизирует синхронизацию с распространенными часами. Он пытается сохранить перекос часов.

Синтез дерева часов

Цель синтез дерева часов (CTS) заключается в минимизации перекоса и задержки вставки. Часы не распространяются до CTS, как показано на рисунке. После CTS провисание должно улучшиться. Дерево часов начинается с определенного источника синхронизации .sdc и заканчивается на стоп-выводах флопа. Есть два типа стопорных штифтов, известных как штифты игнорирования и штифты синхронизации. «Не трогать» схемы и выводы во внешнем интерфейсе (логический синтез) обрабатываются как «игнорируемые» схемы или выводы на заднем конце (физический синтез). Выводы «Игнорировать» игнорируются для анализа времени. Если часы разделены, необходим отдельный анализ перекоса.

- Global Skew обеспечивает нулевой перекос между двумя синхронными выводами без учета логической взаимосвязи.

- Локальный перекос обеспечивает нулевой перекос между двумя синхронными выводами с учетом логической взаимосвязи.

- Если часы намеренно искажены, чтобы уменьшить провисание настройки, это называется полезным перекосом.

Жесткость - это термин, придуманный в Astro для обозначения ослабления ограничений. Чем выше жесткость, тем жестче ограничения.

В оптимизация дерева часов (CTO) часы могут быть экранированы, чтобы шум не попал в другие сигналы. Но экранирование увеличивает площадь на 12-15%. Так как тактовый сигнал является глобальным по своей природе, тот же металлический слой, используемый для маршрутизации питания, используется и для тактового сигнала. CTO достигается за счет выбора размера буфера, размера затвора, перемещения буфера, регулировки уровня и синтеза HFN. Мы стараемся улучшить временные интервалы настройки при предварительном размещении, при оптимизации размещения и пост-размещения перед этапами CTS, игнорируя при этом временное ослабление удержания. При оптимизации размещения постов после CTS уменьшено время удержания. В результате CTS добавлено много буферов. Обычно для 100k гейтов добавляется около 650 буферов.

Маршрутизация

Есть два типа маршрутизация в процессе физического проектирования - глобальная маршрутизация и детальная маршрутизация. Глобальная маршрутизация выделяет ресурсы маршрутизации, которые используются для соединений. Он также отслеживает назначение для конкретной сети.

Подробная маршрутизация делает фактические соединения. Во время маршрутизации необходимо учитывать различные ограничения, такие как DRC, длина провода, время и т. Д.

Физическая проверка

Физическая проверка проверяет правильность созданного макета. Это включает проверку того, что макет

- Соответствует всем технологическим требованиям - Проверка правил проектирования (DRC)

- Соответствует исходному списку соединений - Layout vs. Schematic (LVS)

- Не имеет антенных эффектов - Проверка правил антенны

- Это также включает проверку плотности на уровне всего чипа ... Плотность очистки является очень важным этапом в нижних технологических узлах.

- Соответствует всем электрическим требованиям - Проверка электрических правил (ERC).[6]

Постобработка макета

Постобработка макета, также известная как подготовка данных маски, часто завершается физическим проектированием и проверкой. Он преобразует физическая планировка (многоугольники) в данные маски (инструкции для фотомаска писатель). Это включает в себя[3]

- Обработка стружки, такая как вставка этикеток компании / чипа и окончательных структур (например, уплотнительного кольца, наполнителей),

- Создание макета сетки с тестовыми шаблонами и метками совмещения,

- Подготовка макета к маске, которая расширяет данные макета с помощью графических операций (например, технологии повышения разрешения, RET) и настраивает данные для маскировки производственных устройств (устройство записи фотошаблонов).

Смотрите также

Рекомендации

- ^ Н. Шервани, "Алгоритмы для автоматизации физического проектирования СБИС", Kluwer (1998), ISBN 9780792383932

- ^ А. Канг, Дж. Лиениг, И. Марков, Дж. Ху: "Физический дизайн СБИС: от разбиения графа до закрытия по времени", Springer (2011), Дои:10.1007/978-90-481-9591-6, ISBN 978-90-481-9590-9, п. 7.

- ^ а б Дж. Лиениг, Дж. Шайбле (2020). «Глава 3.3: Данные маски: постобработка макета». Основы топологии электронных схем. Springer. п. 102-110. ISBN 978-3-030-39284-0.

- ^ Полу-нестандартный дизайн

- ^ Мехротра, Алок; Ван Гиннекен, Лукас П. П. П.; Триведи, Ятин. «Схема проектирования и методология для ASIC с шлюзом 50M», Публикации конференции IEEE,ISBN 0-7803-7659-5

- ^ А. Канг, Дж. Лиениг, И. Марков, Дж. Ху: "Физический дизайн СБИС: от разбиения графа до закрытия по времени", Springer (2011), Дои:10.1007/978-90-481-9591-6, ISBN 978-90-481-9590-9, п. 27.